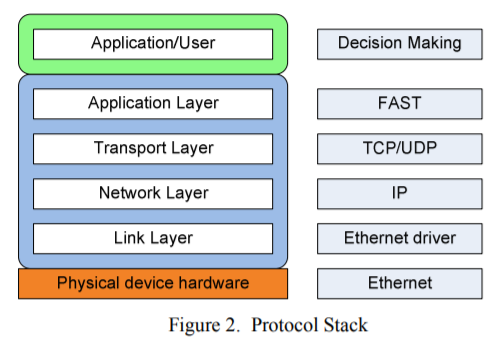

This paper presents the design of an application specific hardware for accelerating High Frequency Trading applications. It is optimized to achieve the lowest possible latency for interpreting market data feeds. The complete system has been implemented in RTL code and evaluated on an FPGA.

HFT trading accelerator engine implemented in Field Programmable Gate Arrays (FPGAs). By using FPGAs we can offload UDP and FAST decoding tasks from the CPU to optimized hardware blocks. Our proposed system implements the complete processing stack except the decision making process in hardware including a highly flexible microcode engine to decode FAST messages. Our approach shows a significant latency reduction of more than 70% compared to the standard software solution while maintaining the flexibility to support new and modified exchange protocols with low efforts in contrast to an Application Specific Integrated Circuit (ASIC) solution

High Frequency Trading Acceleration using FPGAs

Research Report: The Arista 7124FX Switch as a High Performance Trade Execution Platform

Efficient Event Processing through Reconfigurable Hardware for Algorithmic Trading

A Low-Latency Library in FPGA Hardware for High-Frequency Trading (HFT)